# **Closer Look at the New Processor: 80386**

Hamira Shaikh<sup>1\*</sup>, Mosina Shaikh<sup>2</sup>, Shahid Shaikh<sup>3</sup>, Aatif Qureshi<sup>4</sup>, Farman Khan<sup>5</sup>, Viren Patel<sup>6</sup>, Shakila Shaikh<sup>7</sup>, Shiburaj Pappu<sup>8</sup>

<sup>1,2</sup>Dept. of Computer Science, Rizvi College of Engineering, Mumbai, India

<sup>3</sup>Department of Mechanical, Rizvi College of Engineering, Mumbai, India

<sup>4,5,6</sup>Dept. of Computer Science, Rizvi College of Engineering, Mumbai, India

<sup>7,8</sup>Dept. of Computational Sciences and Technology, Rizvi College of Engineering, Mumbai, India

\*Corresponding Author:hamirask492@gmail.com

DOI: https://doi.org/10.26438/ijcse/v7i10.4851 | Available online at: www.ijcseonline.org

#### Accepted: 08/Oct/2019, Published: 31/Oct/2019

*Abstract*—Intel has launched a 32bit microprocessor which was designed for high performance and to drive the most advanced computer-based applications. The 80386 offers the system designer many new and powerful capabilities, including unprecedented performance of 3 to 4 million instructions per second. The addressing modes of 80386 support efficient access to the elements of the standard data structures.

*Keywords*—memory; virtual; instruction; microprocessor;

# I. INTRODUCTION

Intel **80386** is also known as **i386** or just **386**. It was introduced in 1985. It is a 32-bit microprocessor. The architecture of 80286 of 32 bit has been extended to form 80386 with features of instruction set, programming model and binary encoding.

The 32-bit 80386 can properly execute every code made for the earlier 16-bit processors such as 8086 and 80286 that were found in every in PCs. The implementation of 80386 has been proved to be a hundred time faster than the previous processor. In October 1985, 80386 processor was introduced. Significant qualities of chip was manufactured and came in June 1986.The first personal computer to make use of the 80386 was designed and manufactured by Compaq. And marked as the first fundamental component in the IBM PC compatible de facto company and it was updated by a company other than IBM. Main boards for80386-based computer systems were large, heavy, every difficult to use and expensive at first.

Two versions of 80386 are commonly available

#### 1) 80386DX 2)80386SX

80386SX was developed after the DX for the application that didn't require the full 32 bit bus version. It is found in many PCs that same basic motherboard design is used as the 80286.Most application less than the 16MB of memory, so the SX is popular and less costly version of the 80386 microprocessor.

# **II. RELATED WORK**

In [1] this paper we got acquainted by the features of 80386 microprocessor. 80386 has reworked and expanded memory protection support including paged virtual memory and virtual-86 mode, features required at the time by Xenia and UNIX. The memory of 80386 has been proved beneficial for OS/2 and is a fundamental requirement for modern operating systems like Linux, Windows, and Mac OS. There are different clock rates of 80386; the first was 16 MHz with 5 MIPS. Then it got better and better with20 MHz with 6 to 7 MIPS, introduced February 16, 1987 and 25 MHz with 7.5 MIPS, introduced April 4, 1988.The last was 33 MHz with 9.9 MIPS introduced in April 10,1989.It also specified that 80386 has number of transistor.

In [2] this paper, we studied more about 80386 that the Intel 80386 shows the state of the art in high-performance, 32-bit microprocessors. It has absolute object code compatibility with previous processors of the iAPX 86 family of microprocessors, including the 80286, 80186, 80188, 8086, and 8088. This protects major investments in application and operating systems software developed for the iAPX 86 family, while offering a significant enhancement in performance. The 80386's architecture and performance should allow it to be used in a wide range of demanding applications-e.g., in engineering workstations, office systems, robotic and control systems, and expert systems. The 80386 implements a full 32-bit architecture with a 32bit-wide internal data path including registers, ALU, and internal buses; it provides 32-bit instructions, addressing capability, and data types, and a 32-bit external bus interface.

It extends the iAPX 86 family architecture with additional instructions, addressing modes, and data types. It incorporates a complete memory management unit. The 80386 extends the 80286 segmentation model to support four-gigabyte segments and to provide a standard two-level paging mechanism for physical memory management.

In [3] this magazine, it tells that the 80386 microprocessor has more going for it than just 32 bits. Its unique architecture made the machine for mightier than the any mini-computers while lightning the load on programmers. The heart of the microprocessor is its register. From computation of early pc microprocessors i.e. from 8088 to 80286 have used 16bits registers; eight registers of the 80386 are doubled that width, so the work with twice the information in the same time. In addition, these registers can function as 16 bit register in pair to copy perfectly the commands of earlier processors. Besides having a 32 bit data path, the 80386 has 32 bit of addressing so it can directly manipulate 2^32 bytes of memory, a total of 4 gigabytes, In addition, it is design to handle virtual memory that is it can swap bytes form RAM to disk to make programmer to think that it has more space in

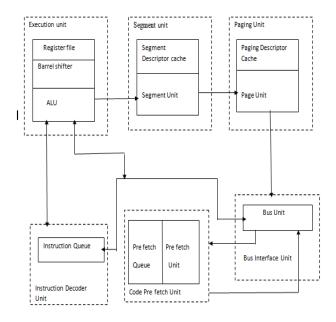

Fig.1.1 Architecture of 80386

RAM than actually exist. Just as with the earlier 80286, which had two operating modes, real and protected, the 80386 has three modes. The first mode is similar but the third mode of this chip is, it can act like one or more 8086 chips that are independent and isolated from one another.

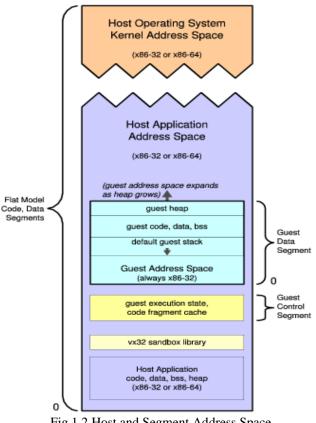

In [4] the x86 design, segmentation is associate address translation step that the processor applies straight off before page translation. additionally to the eight general registers

(GPRs) accessible in user mode, the processor provides six section registers. throughout any operation, the processor uses the worth in one amongst these section registers as associate index into one amongst 2 section translation tables, the world descriptor table (GDT) or native descriptor table (LDT). The GDT historically describes segments shared by all processes, whereas the LDT contains segments specific to a selected method. Upon finding the suitable descriptor table entry, the processor checks permission bits (read, write, and execute) and compares the virtual address of the requested operation against the section limit within the descriptor table, throwing associate exception if any of those checks fail. Finally, the processor adds the section base to the virtual address to make the linear address that it later on uses for page translation. Thus, a standard section with base b and limit 1 permits memory accesses at virtual addresses between zero and 1, and maps these virtual addresses to linear addresses from b to b+l. Today's x86 operational systems generally create segmentation translation a no-op by employing a base of zero and a limit of 232-1. Even during this questionable "flat model," the processor continues to perform segmentation translation: it can not be disabled. Vx32 allocates 2 sections within the host application's LDT for every guest instance: a guest knowledge section and a guest management segment, as pictured in Figure 1.2

#### © 2019, IJCSE All Rights Reserved

# International Journal of Computer Sciences and Engineering

In [5] this paper a general methodology for outlining a micro-chip human, applicable in any high level artificial language, is conferred. An entire set of communication rules is outlined to explain all calls between totally different modules of the emulation software package. The methodology permits development used simple modifications within the human structure to suit totally different processors. Though most analysis is written in pseudo code, associate degree actual implementation is completed in Visual BASIC. Additionally, the projected human is enforced and compared to plain emulators whereas running a typical execution sequence.

# **III. RESULTS AND DISCUSSION**

By studying the specifications of 80386 it was analysed that when confronted with existing DOS application the performance of this processor based pc is simply shocking, erring in the direction of unfulfilled expectation. Even though DOS cannot take advantage of full 32bit instruction set of 80386 the new chip is designed for high operating speed. So with 16bit instruction executing at 16MHz this processor will crunch through numbers twice as fast as an AT. Upcoming versions of this processor will extend its top speed to 29MHz and possibly 24MHz, all with improved performance. As a consequence, even with new computer based on it flooding the market, this processor remains a microprocessor of possibilities. Today it seems to grant the system using it, which will be visible and valuable for processing speed. This processor supports multiprogramming and hence more than one programmer can user the CPU at a time. It increased the virtual memory addressing capabilities from 16mb to 4gb. Therefore this processor works equally with 16bit and 32bit processor. Instruction prefixes that explicitly overrides the default choice of the operand size and address size. Registers can be used for both 16 and 32bit operand and effective address calculation. Thus clock rates has also been increased. This processor has been allowed it to be used in a wide range of demanding applications-e.g., in engineering workstations, office systems, robotic and control systems, and expert systems. It also provides the standard two level paging mechanism for physical memory management.

#### **IV. APPLICATION**

Currently 80386 microprocessor is been used in spaceflight technology and projects. Mobile phones such as Blackberry 950 and Nokia 9000 Communicator uses 80386 processor. The 80386 is currently used in Solar Anomalous Magnetospheric Particle Explorer (SAMPEX) and Hubble Space Telescope (HST).Designed to overcome the limits of its predecessor while maintaining its software compatibility with 8086 and earlier ones. It can be supported by 80387 for mathematical data processing.

# © 2019, IJCSE All Rights Reserved

#### V. CONCLUSION AND FUTURE SCOPE

While launched in 1985, the Intel 80386 was rarely used processor for gaming until early 90's because it was very costly. Regarding future gaming support this processor will not be relevant for the 80's video-games; but from the early 90's until 1994-1995 the 80386 family were compatibles and most used processors for gaming. After comparing between the earlier processors it can be concluded that the introduction of Intel's new 80386SX microprocessor, along with the introduction of Compaq Deskpro 386s computer that uses it, marks advance significant affordable power for PC users. The feature of pipelining, which allows different internal modules of the chip to operate concurrently to speed up its operation further. This processor is a better option during this period in terms of speed and cost. This processor does not have complex design and it features only in highly specialized applications that makes it smaller, easier to produce and cheaper.

#### REFERENCE

- Anup A. Pachghare, G.K. Andurkar, Amruta M. Kulkarni, "A REVIEW ON MICROPROCESSOR AND MICROPROCESSOR SPECIFICATION", International Journal of Science, Engineering and Technology Research (IJSETR) Volume 2, Issue 2, February 2013.

- [2] Khaled El-Ayat, Rakesh K. Agarwal," The Intel 80386-Architecture And Implementation", Published in IEEE Micro 1985DOI:10.1109/mm.1985.304507.

- [3] Ziff Davis," New Coprocessor for new era", PC Magazine February/March 1982.

- [4] Bryan Ford and Russ Cox Massachusetts Institude of Technology"Lightweight, User-level Sandboxing on the x86".

- [5] Zatar, W. Nasr, G.E., 2002, "An Implementation Scheme for a Microprocessor emulator", Otago Univ., Byblos, IEEE.

- [6] https://en.wikipedia.org/wiki/Intel\_80386

- [7] https://whatis.techtarget.com/definition/Intel-80386

- [8] https://css.csail.mit.edu/6.858/2014/readings/i386.pdf

- [9] Magazine: Games vs. Hardware. The History of PC video games

- [10] Tiwari, R. Sam and S. Shaikh, "Analysis and prediction of churn customers for telecommunication industry," 2017 International Conference on I-SMAC (IoT in Social, Mobile, Analytics and Cloud) (I-SMAC), Palladam, 2017, pp. 218-222. doi: 10.1109/I-SMAC.2017.8058343.

- [11] S. Navadia, P. Yadav, J. Thomas and S. Shaikh, "Weather prediction: A novel approach for measuring and analyzing weather data," 2017 International Conference on I-SMAC (IoT in Social, Mobile, Analytics and Cloud) (I-SMAC), Palladam, 2017, pp. 414-417. doi: 10.1109/I-SMAC.2017.8058382.

- [12] S. Shaikh, S. Rathi and P. Janrao, "IRuSL: Image Recommendation Using Semantic Link," 2016 8th International Conference on Computational Intelligence and Communication Networks (CICN), Tehri, 2016, pp. 305-308. doi: 10.1109/CICN.2016.66

- [13] S. Shaikh, S. Rathi and P. Janrao, "Recommendation System in E-Commerce Websites: A Graph Based Approached," 2017 IEEE 7th International Advance Computing Conference (IACC), Hyderabad, 2017, pp. 931-934. doi: 10.1109/IACC.2017.0189

- [14] A. Fasiku, Ayodeji Ireti, B. Olawale, Jimoh Babatunde, C. Abiola Oluwatoyin B., "Comparison of Intel Single-Core and Intel Dual-

*Core Processor Performance*", International Journal of Scientific Research in Computer Science and Engineering, Vol.1, Issue.1, pp.1-9, 2013

- [15] M. Sora, J. Talukdhar, S. Majumder, P.H Talukdhar, U.Sharmah, "Word level detection of Galo and Adi language using acoustical cues", International Journal of Scientific Research in Computer Science and Engineering, Vol.1, Issue.1, pp.10-13, 2013

- [16] Manish Mishra, Piyush Shukla, Rajeev Pandey, "Assessment on different tools used for Simulation of routing for Low power and lossy Networks(RPL)", International Journal of Scientific Research in Network Security and Communication, Vol.7, Issue.4, pp.26-32, 2019

### **Authors Profile**

Hamira Shaikh is pursuing Bachelor of Enginneiring in Computer Engineering from Rizvi college of Engineering which is affialiated with the Mumbai University.

Mosina Shaikh is pursuing Bachelor of Enginneiring in Computer Engineering from Rizvi college of Engineering which is affialiated with the Mumbai University.

Shahid Shaikh is pursuing Bachelor of Enginneiring in Mechanical Engineering from Rizvi college of Engineering which is affialiated with the Mumbai University.

Aatif Qureshi is pursuing Bachelor of Enginneiring in Computer Engineering from Rizvi college of Engineering which is affialiated with the Mumbai University.

Farman Khan is pursuing Bachelor of Enginneiring in Computer Engineering from Rizvi college of Engineering which is affialiated with the Mumbai University.

Viren Patel is pursuing Bachelor of Enginneiring in Computer Engineering from Rizvi college of Engineering which is affialiated with the Mumbai University.