ICSE International Journal of Computer Sciences and Engineering Open Access

**Research Paper**

Volume-4, Issu<u>e-12</u>

E-ISSN: 2347-2693

# Design of a Novel Ring VCO with low Phase Noise and High frequency range

Maryam Taghizadeh<sup>1</sup>, Parisa Taghizadeh<sup>2</sup>, Saeid Taghizadeh<sup>2</sup>,

Abbas Kamaly<sup>2</sup>, Seyed Ali Emamghorashi<sup>2\*</sup>

<sup>1</sup>Department of Electrical Engineering, Fasa Branch, Islamic Azad University, Shiraz, Iran

<sup>2</sup>Department of Electrical Engineering, Fasa Branch, Islamic Azad University, Shiraz, Iran

Available online at: www.ijcseonline.org

| Received: 24/Nov/2016        | Revised: 02/Dec/2016                 | Accepted: 18/Dec/2016                     | Published: 31/Dec/2016    |

|------------------------------|--------------------------------------|-------------------------------------------|---------------------------|

| Abstract— In this pape       | r a ring VCO with high frequency     | y range and low phase noise in 0.18       | um CMOS technology is     |

| presented. In the proposed V | /CO, two techniques including curr   | rent control and forward bias of body i   | s implemented to increase |

| the range of frequency. It i | s shown that forward bias of the b   | ody of control transistor cause to inc    | rease the frequency range |

| noticeably. Moreover, by ac  | lding an inductor in the body of co  | ontrol transistor, the phase noise is dec | reased as well. The phase |

| noise in 1 MHz offset freque | ency is -90 dBc/Hz and the frequence | cy range is 2-14 GHz.                     | -                         |

Keywords- VCO, Ring, Phase noise, Frequency range

#### 1. Introduction

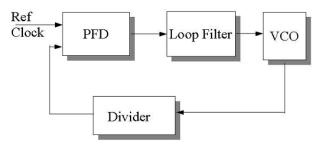

PLL (Phase Locked Loop) has wide range of applications in communication and wireless systems[1]. It can be used for time base generation and synchronization circuits in digital ICs as well as phase detection and demodulation in analog circuits[1]. Figure 1 shows the block diagram of a PLL circuit. The heart of a PLL is voltage controlled oscillator (VCO) that can be implemented using LC or ring oscillators [2, 3].

LC oscillators use small value of capacitor and inductor [4] which usually have low quality factor. The low quality factor causes large phase noise and narrow tuning range. Therefore, LC oscillators are mostly used in high phase noise and narrow tuning range applications[5]. Furthermore, large spiral inductors consume a large chip area that is not desirable for integration.

Figure1. A typical PLL circuit block diagram

Ring voltage controlled oscillators (RVCO) have lower phase noise than LC oscillators and because of the wide tuning range, they are used in PLL circuits. In addition,

© 2016, IJCSE All Rights Reserved

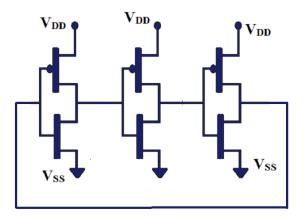

because of smaller chip area comparing to LC oscillators, it is easier to integrate them in a CMOS technology. A ring oscillator consists of multiple gain stages (delay cells) in a loop [4,6] as shown in Figure 2. Different delay cells have been compared in terms of different parameters such as tuning range, power dissipation and phase noise. The delay cells can be differential or single-ended units.

Differential configuration is more common because of common mode noise rejection capability, but uses larger chip area and consume more power[3]. The challenges in the RVCO design are to achieve linearity of frequency modulation, low voltage and power Consumption, low phase noise and wide frequency range [7].

Figure 2 A ring oscillator consists of multiple delay cells

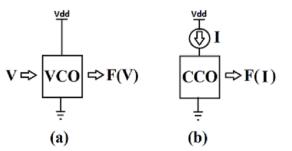

A single-ended oscillator should contain odd number of delay/gain stages with  $\pi/n$  delay value for each stage in a feedback loop [8]. Most reported designs use single ended or differential configuration using current controlled (CC) or voltage controlled (VC) technique as shown in figure 3[4,9].

Figure 3. (a) voltage-controlled oscillator. (b) currentcontrolled oscillator [9]

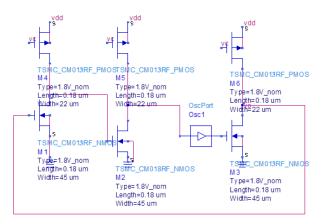

A typical Ring VCO is plotted in Figure 4. In this design, the voltage control Vc is used to control the frequency of oscillator.

Figure 4. A typical Ring VCO

In this paper the current controlled method with body biasing technique have been used to decrease the threshold voltage Vth and improve the RVCO performance. Single-ended circuit has been simulated to present the concept, even though, the method can be extended to differential pair configuration.

This paper has been structured as follows, section 2 describes RVCO circuit design, transistor sizing and oscillation frequency. Simulation and analysis of the circuit are in section 3. Concluding remarks are at the end.

## 2. Proposed topology

The method used here is based on changing bulk voltage to change the current of oscillator and so the wider range og gate voltage control could be achieved.

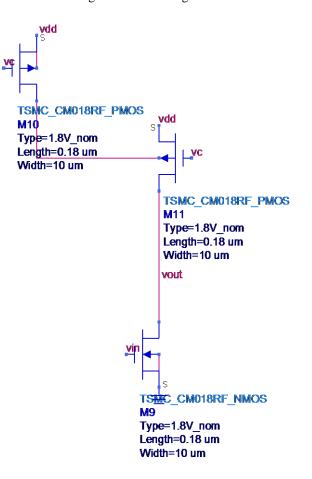

In this paper the three stage oscillator with current control method is used. Increasing the number of stages can cause to decrease the frequency of oscillatuion and increase of power consumption. Figure 5 shows one stage of ring oscillator. In this design the body of control transistor is biased to increase the range of current variatons. The bulk voltage of the PMOS transistor should be controlled in a way that the bulk-source junction remains in reverse or slightly into forward bias. To guarantee this the bulk-source junction will not go into forward bias more than 0.5V, so the bulk current will remain negligibly low [5, 10]. An extra transistor M10 has been used to better control the bulk voltage and reduce loading effects on the control voltage as shown in Figure 5.

Figure 5 one stage of ring oscillator

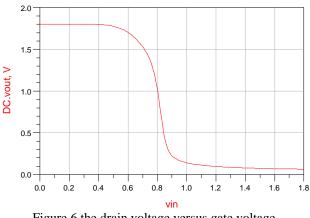

Figure 6 shows the drain voltage versus gate voltage of one stage delay cell for Vc=0.5 V

Figure 6 the drain voltage versus gate voltage

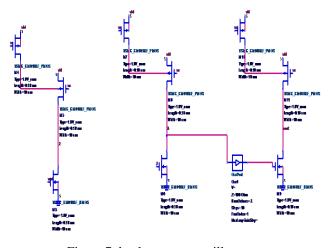

Figure 7 shows the three stage oscillator. The frequency of this oscillator is as follows:

$$f_{osc} = \frac{1}{6C_{load}V_{DSn}} \left(\frac{1}{2}K_p \left(\frac{w}{l}\right)_p \left(V_{DD} - V_{in} - \left|V_{THp}\right|\right)^2\right)$$

(1)

$$\left|V_{THp}\right| = \left|V_{TH0p}\right| + \gamma \left(\sqrt{2\left|\Phi_{f}\right| - V_{sb}} - \sqrt{2\left|\Phi_{f}\right|}\right)$$

(2)

This equation shows that the oscillation frequency is decreased by increasing the control voltage.

Figure 7 the three stage oscillator

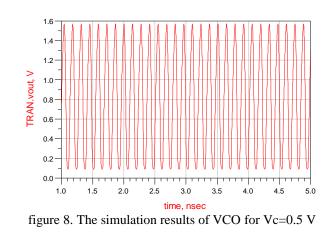

The simulation results of this circuit is shown in figure 8 for Vc=0.5 V. in this state the oscillation frequency is 7.14 GHz.

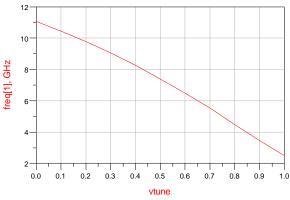

The oscillation frequency as a function of voltage control is plotted in figure 9. As voltage control is changed from 0 to 1 v, the frequency is changed from 1.75 GHz to 11 GHz.

Figure 9. The oscillation frequency as a function of voltage control

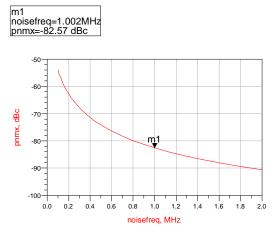

The phase noise of this oscillator for Vc=0.5 V is plotted in Figure 10. One can see that the phase noise of this oscillator in this state is -82.5 dBc/Hz.

Figure 10. The phase noise of this oscillator for Vc=0.5 V

## International Journal of Computer Sciences and Engineering

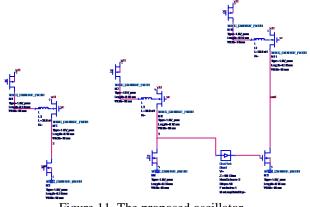

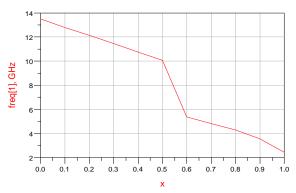

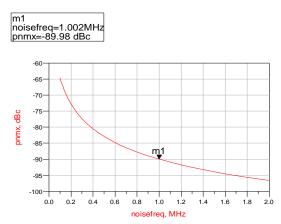

To improve the performance of proposed oscillator, an inductor is added in the bulk of control transistor. The proposed oscillator is shown in figure 11. Figure 12 shows the frequency range of proposed oscillator. One can see that the frequency range of proposed oscillator is increased by 3 GHz. The phase noise of proposed oscillator is shown in figure 13. One can see that the phase noise of proposed oscillator is improved noticeably. Table 1 shows the results of proposed oscillator.

Figure 11. The proposed oscillator

Figure 12 the frequency range of proposed oscillator

Figure 13 the phase noise of proposed oscillator

Vol.-4(12), Dec 2016, E-ISSN: 2347-2693

| Power consumption |         | Frequency range Phase |        |        | noise |

|-------------------|---------|-----------------------|--------|--------|-------|

| ref               | 1 27 4  | CII-                  | 05 10  | - /I I | [1]   |

| -14 dB            | 1.27-4  | -                     | -85 dB |        | [1]   |

| -7 dB 3.6-6.2     |         |                       |        | [2]    |       |

| -8.5 dB           | 4.7-9.3 |                       | -92 dB |        | [3]   |

| -14 dB            | 2-14 G  | Hz                    | -90 dB | sc/Hz  | This  |

| work              |         |                       |        |        |       |

## 3. Conclusion

In this paper, a novel ring oscillator is proposed and simulated in 0.18 um cmos technology. To increase the frequency range of oscillator a novel technique based on forward bias of body of control transistor is proposed. Moreover, an inductor is added to the bulk of control transistor to improve its performance. It is shown that by using inductor the frequency range and phase noise is improved simultaneously. The phase noise of proposed oscillator was -90 dBc/Hz and the frequency range was 2-14 GHz.

### References

- M.-L. Sheu, Y.-S. Tiao, L.-J. Taso, "A 1-V 4-GHz wide tuning range voltage-controlled ring oscillator in 0.18μm CMOS," Microelectronics Journal, vol. 42, pp. 897-902, 2011.

- [2] J. Zhao and Y.-B. Kim, "A low-power digitally controlled oscillator for all digital phase-locked loops," VLSI Design, vol. 2010, p. 2, 2010.

- [3] W.-H. Lee, B.-J. Gu, Y. Nishida, H. Takao, K. Sawada, M. Ishida, "Oscillation-controlled CMOS ring oscillator for wireless sensor systems," Microelectronics Journal, vol. 41, pp. 815-819, 2010.

- [4] M. Frankiewicz and A. Kos, "Wide-frequency-range low-power variable-length ring oscillator in

- UMC CMOS 0.18 μm," in Mixed Design of Integrated Circuits and Systems (MIXDES), 2013 Proceedings of the 20th International Conference, 2013, pp. 291-293.

- [5] T. Li, B. Ye, J. Jiang, "0.5 V 1.3 GHz voltage controlled ring oscillator," in ASIC, 2009. ASICON'09. IEEE 8th International Conference on, 2009, pp. 1181-1184.

- [6] U. Guler and G. Dundar, "Modeling CMOS Ring Oscillator Performance as a Randomness Source," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 61, pp. 712-724, 2014.

- [7] T. V. Cao, D.T. Wisland, T.S. Lande, F. Moradi, "A bulk-controlled ring-VCO with 1/f-noise reduction for frequency  $\Delta\Sigma$  modulator," in Mixed Design of Integrated Circuits & Systems, 2009.

MIXDES'09. MIXDES-16th International Conference, 2009, pp. 187-192.

- [8] A. Ramazani, S. Biabani, GH. Hadidi, "CMOS Ring Oscillator with Combined Delay Stages," AEU-International Journal of Electronics and Communications, 2014.

- [9] P. Nugroho, R.K. Pokharel, H. Kanaya, K. Yoshida, "A 5.9 GHz Low Power and Wide Tuning Range CMOS Current-controlled Ring Oscillator," International Journal of Electrical and Computer Engineering (IJECE), vol. 2, pp. 293-300, 2012.

- [10] J. Radic, A. Djugova, L. Nagy, M. Videnovic-Misic, "Body effect influence on 0.18 μ m CMOS ring oscillator performance for IR-UWB pulse generator applications," in Embedded Computing (MECO), 2012 Mediterranean Conference on, 2012, pp. 170-173.

- [11] J. Garg and S. Verma, "Design of low power Voltage Controlled Oscillator," in Emerging Technology Trends in Electronics, Communication and Networking (ET2ECN), 2012 1st International Conference on, 2012, pp. 1-4.

- [12] R. Ashish, J.N. Vashishtha, R K sarin, "A RF Low Power 0.18-μ m based CMOS Differential ring oscillator," Proceedings of the World Congress on Engineering, vol. 2, 2012.

- [13] S.-M. Kang and Y. Leblebici, CMOS digital integrated circuits: Tata McGraw-Hill Education, 2003.

- [14] A. Daghighi and A. Neshat-Niko, "VCO Design and Simulation Using TSMC 0.18 um Process to Meet IEEE802.11a Requirements," Majlesi Journal of Electrical Engineering, vol. 2, pp. 29-37, 2008.

- [15] S. Shieh Ali Saleh and N. Masoumi, "Wide-tuningrange, low-phase-noise quadrature ring oscillator exploiting a novel noise canceling technique," AEU

International Journal of Electronics and Communications, vol. 66, pp. 372-379, 2012.

- [9] Jian ZhangI;Guoch Huang," SiGe V Band Wide Tuning-Range vco and Frequency Divider for Phase Locked Loop", Integrated Nonlinear Microwave and Millimetre-Wave Circuits (INMMIC), Sept. 2012,pp(1 - 3), E-ISBN :978-1-4673-2948-4