# Low Noise Amplifier with Low Power Consumption in 0.18 Micrometer CMOS Technology

# Majid. Haghi<sup>1</sup>, Mohammad. Emadi<sup>2\*</sup>

<sup>1</sup>Dept. of Cyber Security Management, Department of Security, National Defense univercity, Cyber space), and Active in ICT Field, Iran

<sup>2</sup>University Lecturer and Active in ICT Field, Iran

\*Corresponding Author: mohammad.emadi24@gmail.com Tel.: +98-9199066614

DOI: https://doi.org/10.26438/ijcse/v7i10.18 | Available online at: www.ijcseonline.org

Accepted: 07/Oct/2019, Published: 31/Oct/2019

Abstract: In this paper we present a new model of low noise amplifier and propose solutions to improve performance. Both single-head and two-head amplifiers are designed and simulated with common mode feedback circuit.

Keywords: noise, amplifier, power, CMOS Technology

# I. INTRODUCTION

### **Two-stage amplifier**

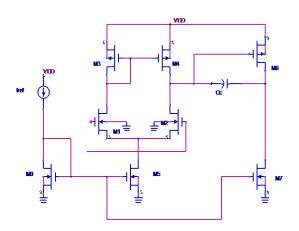

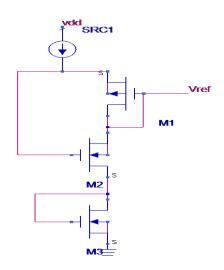

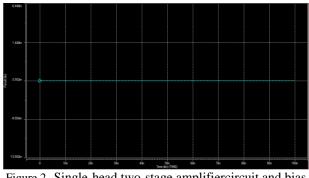

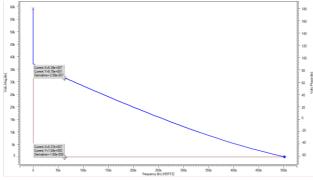

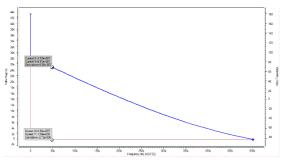

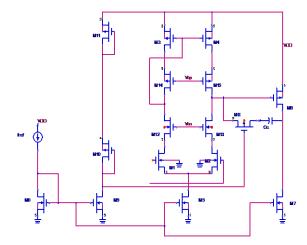

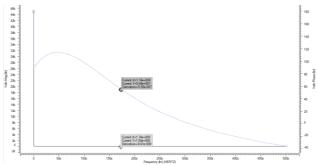

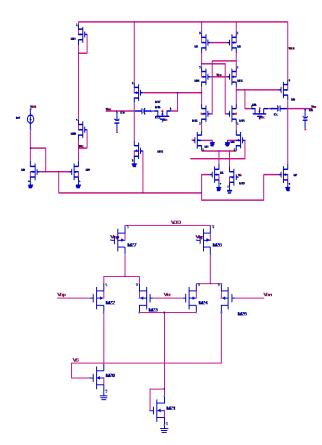

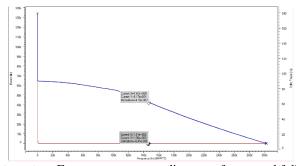

First, we design and simulate single-head amplifier circuit according with circuit drawn in Figure 1.In this figure, bias circuit is also plotted. Wherever a bias circuit is needed, this circuit is used by default. Calculating W / L values manually then optimizes them to meet the needs.Designed and simulated in 0.18 um CMOS technology and with HSPICE software.The amount of power consumption is shown in Figure 2.It can be seen power consumption of this amplifier is 3.55mA. It is shown frequency response of this amplifier in Figure 2. It can be seen gain is equal to 60000 or 95 dB, cut-off frequency is 63.7 MHz, and phase margin is 67 degrees.

Figure 1. Single-head two-stage amplifiercircuit and bias circuit schematics.

Figure 2. Single-head two-stage amplifiercircuit and bias circuit schematics

Figure 3. Two-stage amplifier frequency response plot.

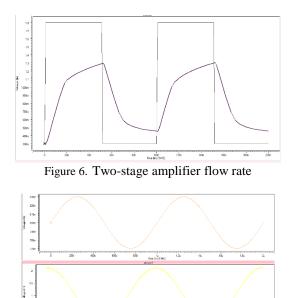

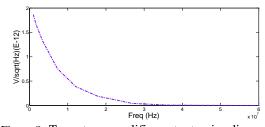

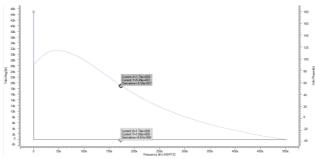

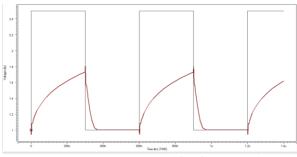

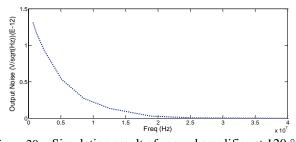

These simulations are provided at room temperature and tt corner. It is simulated circuit at other temperatures and corners To survey effect of temperature and process and is presented the results. It is shown simulation results at 120 °C and ss corner in Figure 4. It can be seen gain and bandwidth have dropped sharply in this mode. gain, cut-off frequency and phase margin are 44000 or 92 dB, 49 MHz and 69 degrees, respectively. In Figure 5 is shown simulation results at -40 ° C and ff corner. In this mode, gain, cut-off frequency and phase margin are 650,000, 80 MHz and 65.5 degrees, respectively. Figures 6 and 7 are shown flow rate and swinging charts for this amplifier at room temperature and tt corner, respectively. By calculating slope of output changes, flow rate is equal to calculating slope of output changes, flow rate is 35 V / us and the swing is 2.1 V. Figure 7 is shown output noise diagram of this amplifier. It can be seen maximum output noise is 2E-12 V / sqrt (Hz). Table1 is summarized design results of this amplifier.

Figure 4. Simulation results at 120°C and ss corner.

Figure 5. Simulation results at -40 °C and ff corner

Figure 7. Two-stage amplifier swing diagram

Figure 8. Two-stage amplifier output noise diagram

| Table 1. Single-headed two-stage amplifier simulation results |        |        |        |  |  |

|---------------------------------------------------------------|--------|--------|--------|--|--|

|                                                               | tt, 25 | ss,120 | ff,-40 |  |  |

| Gain(dB)                                                      | 95     | 92     | 96     |  |  |

| Cut-off frequency (MHz)                                       | 63     | 49     | 80     |  |  |

| Phase margin                                                  | 67     | 68     | 65     |  |  |

| flow rate (V/us)                                              | 35     | 43     | 31     |  |  |

| swing (V)                                                     | 2.1    | 1.9    | 2      |  |  |

| <b>Power consumption</b> ( <b>mW</b> )                        | 3.5    | 3.5    | 3.5    |  |  |

| Output noise V/sqrt(Hz)(E-<br>12)                             | 2      | 1.8    | 2.4    |  |  |

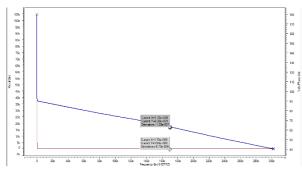

To improve frequency response, it is used a resistor at capacitive compensation path. This resistor creates a zero and improves the frequency response. This has no effect on gain and power consumption and only improves bandwidth. Figure 9, 10 are shown schematic of circuit and simulation result, respectively. it can be seen From figure 10 frequency response has had a significant improvement, but output noise has increased to 3.5. Voltage gain has not changed, but cut-off frequency has increased to 232 MHz.simulation results of this structure at various temperatures and corners are presented in Table 2. It can be seen at 120 ° C - ss corner and cut-off frequency is unit and at -40 °C-ff corner, phase

# International Journal of Computer Sciences and Engineering

## Vol. 7(10), Oct 2019, E-ISSN: 2347-2693

margin is spoiled. To solve this problem, it is necessary tokeepconstant bias current, by changing temperature and corner, and also instead of resistor, a transistor should be used, because resistor is very sensitive to temperature.

Figure 9. Use compensation resistor to improve frequency response.

Figure 10. Frequency Response and Two-Stage amplifier Noise Using compensation resistor.

Table 2. Results of single-headed two-stage amplifier simulation with compensating resistor

|                              | tt, 25 | ss,120 | <b>ff,-40</b> |

|------------------------------|--------|--------|---------------|

| Gain(dB)                     | 95     | 92     | 96            |

| Cut-off frequency (MHz)      | 232    | 162    | 324           |

| Phase margin                 | 62     | 92     | 45            |

| flow rate (V/us)             | 35     | 43     | 31            |

| swing (V)                    | 2.1    | 1.9    | 2             |

| <b>Power consumption(mW)</b> | 3.5    | 3.5    | 3.5           |

Figure 11 is suggested to solve problem of temperature and corner. In this circuit, transistors are used instead of resistor. Transistors  $M_{9-11}$  have been used for bias of transistor  $M_8$ . Transistors  $M_{12-15}$  are also used to increase gain and bandwidth.

Figure 11. Proposed Single-headed two-stage amplifier

Figure 12 is illustrated simulation results of this circuit at room temperature and tt corner. gain, cut-off frequency and phase margin of circuit are 95 dB, 209 MHz, and 62 degrees, respectively. It can also be seen output noise is significantly reduced compared to the previous circuit, due to removal of resistor.

Figure 12. Simulation result of circuit Figure.11 at room temperature and tt corner.

#### © 2019, IJCSE All Rights Reserved

Figures 13 and 14 are shown simulation results at 120°C,ss corner and 40 °C,ffcorner. It can be seen results changes at different temperatures and corners are negligible. Table 3 is presented results of this design. Figures 15 and 16 are shown flow rate and proposed amplifier swing, respectively.

Figure 13. Simulation result of circuit Figure11 at room temperature and tt corner.

Figure 14. Simulation result of circuit Figure 9 at -40 °C and the ff corner.

Figure 15. Recommended amplifier flow rate diagram.

Figure 16. Proposed amplifier swing diagram.

© 2019, IJCSE All Rights Reserved

Table 3: Simulation results of single-headed two-stage amplifier with compensator resistor

|                         | tt, 25 | ss,120 | ff,-40 |  |  |

|-------------------------|--------|--------|--------|--|--|

| Gain(dB)                | 95     | 93.2   | 95     |  |  |

| Cut-off frequency (MHz) | 209    | 174    | 260    |  |  |

| Phase margin            | 62     | 55     | 65     |  |  |

| flow rate (V/us)        | 68     | 72     | 62     |  |  |

| swing (V)               | 2.4    | 2.2    | 2.1    |  |  |

| Power consumption(mW)   | 3.5    | 3.5    | 3.5    |  |  |

| Output noise            | 1.8    | 2      | 2.1    |  |  |

Proposed circuit changes at various temperatures and corners are negligible and this amplifier fulfills design requirements at all temperatures and corners.

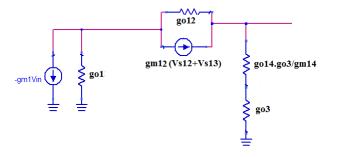

One of the most important parameters of amplifier is its voltage gain. Researchers are always trying to increase gain of amplifier without breaking other parameters. To increase voltagegain is recommendcircuit of Figure 17. In this circuit, gate of transistors M12, 13 are connected to the M3, 4 drains instead of connected to a fixed bias.In fact, we have used cross-linking in this structure. This cross-linked connection generates a positive feedback loop that increases voltage gain. To illustrate reason for this increase, we plot proposed small signal model. First stage Small signal model of second proposed scheme, which includes a cross-linked connection, is plotted in Figure 18. With small signal model, voltage gain of the proposed circuit is as follows:

$$A_V = \frac{g_{m1}.(g_{012} - g_{m12})}{g_{01}(\frac{g_{m12}g_{014}}{g_{m14}})(\frac{g_{03}}{g_{01}} + 1) - g_{01}g_{012}} \qquad \square \square$$

Assuming  $g_{o1} = g_{o3}$  and  $g_{m1} > g_{o1}$ , DC voltage gain will be equal to:

Figure 17. second proposed amplifier circuit

Figure 18. second proposed small signal model

Considering this relationship, if  $\frac{g_{m12}g_{o14}}{g_{m14}} = g_{o12}$ , the

amplifier voltage gain will be unlimited.

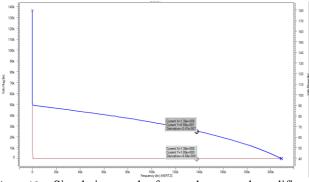

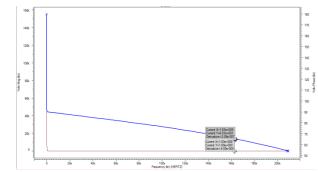

Figure 19 is shown simulation result of this circuit.It can be seen gain has almost doubled to 140,000 or 103dB. cut-off frequency unit and phase margin are 138 MHz and 65 °, respectively. Figures 20 and 21 are shown simulation results at 120°C, ss corner and -40°C, ffcorner. It can be seen result changes at different temperatures and corners are negligibleand circuit operation is not damaged.In addition, output noise has decreased significantly and dropped to 1.2.At temperature of120 °C and sscorner, cut-off frequency and phase margin are 100 dB, 113 MHz and 66 °, respectively. At temperature of -40 °C andffcorner, these results are 104 dB, 163 MHz and 65 ° respectively.

Figure 19. Simulation result of second proposed amplifier at room temperature and tt corner.

Figure 20. Simulation result of second amplifier at 120 °C and ss corner.

Figure 21. Simulation result of second proposed amplifier at -40 °C and ff corner.

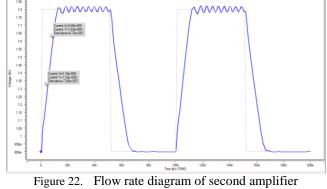

Figures 22 and 23 are shown flow rate diagram and proposed second amplifier swing, respectively. It can be seen flow rate has significant improvement (74 V/us).

Table 4 summarizes simulation results of second proposed amplifier.

Figure 23. Second proposed amplifier swinging diagram

| Table 4. SimulationResult of second | proposed amplifier |

|-------------------------------------|--------------------|

|-------------------------------------|--------------------|

|                                        |        | 1 1    | 1      |

|----------------------------------------|--------|--------|--------|

|                                        | tt, 25 | ss,120 | ff,-40 |

| Gain(dB)                               | 103    | 100    | 104    |

| Cut-off frequency (MHz)                | 138    | 113    | 163    |

|                                        |        |        |        |

| Phase margin                           | 65     | 66     | 65     |

| flow rate (V/us)                       | 74     | 78     | 73     |

| swing (V)                              | 2.4    | 2.2    | 2.1    |

| <b>Power consumption</b> ( <b>mW</b> ) | 3.7    | 3.7    | 3.7    |

| Output noise                           | 1.2    | 1.32   | 1.24   |

|                                        |        |        |        |

Vol. 7(10), Oct 2019, E-ISSN: 2347-2693

# II. FULLY TWO-STAGE DIFFERENTIAL AMPLIFIER

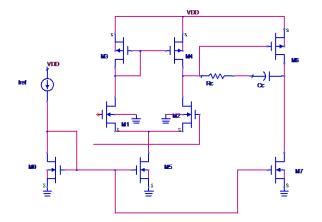

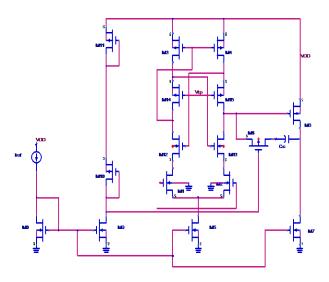

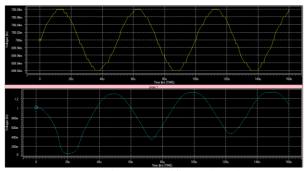

To eliminate ambient noise and power supply noise, fully differential amplifiers can be used. These amplifiers also have higher gain in addition to noise elimination. In this section, based on proposed second circuit, we present and design a fully differential circuit. Fully differential amplifiers also need a common mode feedback circuit. It is suggested and designed a structure in this circuit. Figure 24 is shown proposed fully differential amplifier circuit along with proposed common mode feedback circuit.

Figure 24. Proposed differential amplifier circuit with a common mode feedback circuit.

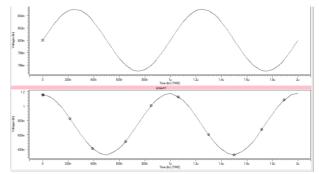

Here Here  $V_{cr}$  and  $V_{bp}$  are bias voltages. Operation of common-mode feedback circuit ,if the output voltage come to the triode, for example Vop and Vonarereduced, Vs is increased.As a result, source voltage M1,2are reduced, and consequently the drain voltage M6,17are reduced, thus output voltage increases.In this way, this circuit stabilizes output voltage in the middle of the supply. Figure 25 is shown frequency response diagram of proposed fully differential amplifier atroom temperature and ttcorner. It can be seen proposed voltage gain is 104 dB, cut-off frequency is 140 MHz and phase margin is 64 degrees.Figures 26 and 27

are shown simulation results at  $120^{\circ}$ C, ss corner, and -40 °C, ff corner, respectively. It can be seen at temperature of 120 °C and ss corner, cut-off frequency and phase margin are 102 dB, 147 MHz and 61 degrees, for temperature of -40 °C and ff corner, 102 dB, 170 MHz and 63 degrees, respectively.

Figure 25. Frequency response diagram of proposed fully differential amplifier at room temperature andtt corner

Figure 26. Frequency response diagram of proposed fully differential amplifier at 120°Cand ss corner

Figure 27. Frequency response diagram of proposed fully differential amplifier at-40°C and ff corner

# International Journal of Computer Sciences and Engineering

Figure 28 is shown ultimate amplifier flow rate. It can be seen flow rate is 160 V / us. Figure 29 is shown swing diagram of this amplifier. simulation results of this amplifier are summarized in Table 5. Table 6 is compared results of this research with previous work.

Figure 28. Ultimate amplifier flow rate diagram

Figure 29. Ultimate amplifier swing diagram

| Table 5: results of two-stage differential amplifier | r |

|------------------------------------------------------|---|

| simulations                                          |   |

|                              | tt, 25 | ss,120 | ff,-40 |

|------------------------------|--------|--------|--------|

| Gain(dB)                     | 104    | 102    | 102    |

| Cut-off frequency (MHz)      | 140    | 147    | 170    |

| Phase margin                 | 62     | 61     | 63     |

| flow rate (V/us)             | 160    | 168    | 157    |

| swing (V)                    | 1      | 0.9    | 1.1    |

| <b>Power consumption(mW)</b> | 60     | 62     | 61     |

| Output noise                 | 1.2    | 1.32   | 1.24   |

Table 6 Differential Two-stage Amplifier Simulation Results

|                            | [4]  | [13]  | [16] | [17] | This<br>research |

|----------------------------|------|-------|------|------|------------------|

| Gain(dB)                   | 98   | 67.7  | 82   | 65   | 104              |

| Cut-off frequency<br>(MHz) | 60   | 91    | 3.6  | 0.75 | 148              |

| Phase margin               | 60   | 55    | 80   | 50   | 61               |

| flow rate (V/us)           | 154  | NA    | NA   | NA   | 160              |

| swing (V)                  | NA   | NA    | NA   | NA   | 1.6              |

| Power<br>consumption(mW)   | NA   | 0.234 | NA   | NA   | 60               |

| Output noise               | 2.49 | 1.75  | NA   | NA   | 1.2              |

#### **III. CONCLUSION**

In this paper, we study design of single-head and differential amplifier circuits and also common mode feedback circuits. Then we began to design low-noise amplifier with low power consumption circuits. Initially, it is designed and simulated simple two-stage single-head amplifier circuit. Calculate the W / L values by hand analysis and then optimize it to meet the needs. Designed and simulated in 0.18 um CMOS technology and simulated with HSPICE software. gain voltage was 89 dB, cut-off frequency was 47 MHz, and phase margin was 69 °. In this study, we also simulated results at various temperatures and corners. We tried to design a circuit in all conditions, the results would be appropriate and acceptable. We used a resistor at capacitance compensator path to improve frequency response. This resistor creates a zero and improves frequency response. It was seen this resistor does not have an effect on gain and power consumption, and only improves bandwidth and also frequency response had a significant improvement. With this technique, cut-off frequency was increased to 252 MHz.

To solve problem of temperature and corner, it was used a transistor instead of resistor. It was seen with this technique, results changes are very inconsiderable at different temperatures and corners. In the next step, it wasintroduced a new structure to increase voltage gain, which has a crosslinked connection. In fact, this cross-linked connection generated a positive feedback that increased voltage gain. To illustrate the reason for this increase, it was plotted proposed small signal model and indicated that the proposed structure could have high voltage gain. Finally, to reduce the ambient noise, it was proposed a structure as a fully differential and a common mode feedback circuit.

### REFERENCES

- [1] Hitoshi I, Tomoyuki O, Masanori T, et al. "An auto-gain control trans-impedance amplifier with low noise and wide input dynamic range for 10-Gb/s optical communication systems", IEEE J Solid-State Circuits, Vol. 36(5), pp. 1303, 2001.

- [2] Han Peng, Wang Zhigong, Sun Ling, et al. "155Mb/s automatic gain control CMOS trans-impedance preamplifier for optical communication", ACTA Electronica Sinica, Vol. 35(11), pp. 2189, 2007.

- [3] Yu Changliang, Mao Luhong, Xiao Xingdong, "Standard CMOS Implementation of a novel, fully differential optoelectronic integrated receiver", Chinese Journal of Optoelectronics Laser, Vol. 20(4), pp. 432, 2009.

- [4] Huang Beiju, Zhang Xu, Chen Hongda. "1-Gb/s zero-pole cancellation CMOS trans-impedance amplifier for Gigabit Ethernet applications", Journal of Semiconductors, Vol. 30(10), 1, 2009.

- [5] Chen W Z, Cheng Y L, Lin D S. "A 1.8-V 10-Gb/s fully integrated CMOS optical receiver analog front-end", IEEE J Solid-State Circuits, Vol. 40(6), pp. 1388, 2005.

- [6] Jin J D, Hsu S H. "A 75-dB 10-Gbps trans-impedance amplifier in 0.18-\_m CMOS technology", IEEE Photonics Technol. Lett, Vol. 20(24), 2177, 2008.

#### © 2019, IJCSE All Rights Reserved

#### International Journal of Computer Sciences and Engineering

- [7] Chen W Z, Huang S H. "A 2.5 Gbps CMOS fully integrated optical receiver with lateral PIN

- detector", Proc IEEE Custom Integrated Circuits Conference, 293, 2007.

- [8] B. Razavi, "Design of integrated circuits for optical communications", Wiley series in lasers and applications, 2nd edition, 2003.

- [9] M. Rakideh, M. Seifouri, P. Amiri, "A folded cascode-based broadband transimpedance amplifier for optical communication", Microelectronics Journals, Vol. 54, pp. 1–8, 2016.

- [10] D. Chen, S. Yeh, X. Shi, M.A. Do, C.C. Boon, W.M. Lim, "Crosscoupled current conveyor based CMOS transimpedance amplifier for broadband data transmission", IEEE Trans. Very Large Scale Integer. (VLSI) System, Vol. 21, pp. 1516–1525, 2013.

- [11] M.H. Taghavi, L. Belostotski, J.W. Haslett, P. Ahmadi, "10-Gb/s 0.13-µm CMOS inductor less modified-RGC transimpedance amplifier", IEEE Transactions on Circuits and Systems, Vol. 62, pp. 1971–1980, 2015.

- [12] P. Andre, S. Jacobus, "Design of a high gain and power efficient optical receiver front-end in 0.13μm RF CMOS technology for 10Gbps applications", Microw. Opt. Technol. Lett., Vol. 58, pp. 1499–1504, 2016.

- [13] K. Honda, H. Katsurai, M. Nada, "A 56-Gb/s transimpedance amplifier in 0.13-µm SiGe BiCMOS for an optical receiver with -18.8dBm input sensitivity", in: Proceeding of the IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), 2016.

- [14] M. Seifouri, P. Amiri, I. Dadras, "A transimpedance Amplifier for optical communication network based on active voltage-current feedback", Microelectronics Journal, Vol. 67, pp. 25-31, 2017.

- [15] Y. Chen, J. Li, Z. Zhang, H. Wang, Y. Zhang, "12-Channel, 480 Gbit/s optical receiver analogue front-end in 0.13µm BiCMOS technology", Electron. Lett., Vol. 53, pp. 492-494, 2017.

- [16] Y. Akbey and O. Palatmutcuogullari, "A Broadband Differential Transimpedance Amplifier in 0.35µm SI Ge BICMOS Technology for 10Gb/S Fiber Optical Front Ends", Analog integrated Circuits and Signal Processing, Vol. 74, Issue. 1, pp.155-162, 2013.

- [17] R.Y. Chen, Z.Y. Yang, "CMOS transimpedance amplifier for gigabit-per-second optical wireless communications", IEEE Trans. Circuits Syst. II, Vol. 63, pp. 418–422, 2016.